## Paris Session 2022

Requirements on the design and testing of RC voltage dividers for application in HVDC GIS SC D1 – Materials and emerging test techniques PS 1 – Testing, monitoring and diagnostics Question 1.03 – Gas-insulated voltage dividers for HVDC application Maria KOSSE, Dr. Ing. (Germany), Erik SPERLNG, Dr.-Ing. (Switzerland)

© CIGRE 2022

# Requirements on the design and testing of RC voltage dividers for application in HVDC GIS

- Worldwide development activities on HVDC GIS with products available up to  $U_r = \pm 550 \text{ kV DC}$

- Standardization for HVDC GIS prepared with CIGRE TB 842

- Additional thermo-electric tests to consider DC specifics in terms of electric field distribution of insulators, influenced by the accumulation of electrical charge carriers and the inhomogeneous temperature distribution

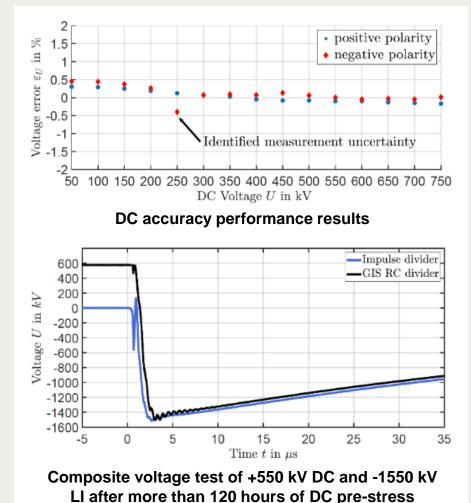

- High importance: composite voltage testing (DC + impulse) after long DC pre-stress (reaching DC steadystate) with maximum temperature gradient

- Standardization for low-power instrument transformers within IEC 61869 series

### Analysis of existing CIGRE recommendations and IEC standards

- Requirements for AC and DC withstand voltage tests are comparable

- Requirements for LI voltage tests are the same. SI voltage test acc. IEC 61869-15 only with positive voltage, while acc. CIGRE TB 842 for both polarities

- Composite voltage tests not existing acc. IEC 61869-15. According to TB 842, composite voltage tests ensure appropriate insulation performance under transient overvoltages during operation

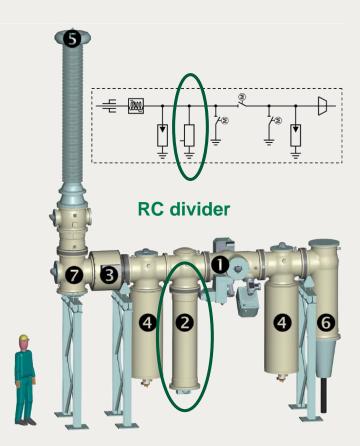

| Equipment U <sub>r</sub> = U <sub>m</sub> =                                         | : ±550 kV             | DC GIS                                          | RC divider   |

|-------------------------------------------------------------------------------------|-----------------------|-------------------------------------------------|--------------|

| Standard                                                                            |                       | CIGRE TB 842                                    | IEC 61869-15 |

| DC withstand                                                                        | U <sub>DC</sub> / kV  | $1.5 \text{xU}_{\text{r}} = \pm 825 \text{ kV}$ |              |

| voltage test                                                                        | t <sub>DC</sub> / min | 1                                               | 60           |

| AC withstand                                                                        | u <sub>AC</sub> / kV  | 1.5xU <sub>r</sub> /√2 = 583 kV                 |              |

| voltage test                                                                        | t <sub>AC</sub> / min | 1                                               |              |

| Impulse                                                                             | Û <sub>LI</sub> / kV  | ±1550                                           |              |

| voltage test                                                                        | Û <sub>SI</sub> / kV  | ±1175                                           | +1175        |

| (not mandatory                                                                      | # impulse             | 15 per polarity                                 |              |

| for DC GIS)                                                                         | I <sub>n</sub> / A    | 0                                               | 0            |

| Superimposed<br>impulse voltage<br>test<br>("Uncharged" di-<br>electric interfaces) | U <sub>DC</sub> / kV  | ±550                                            | Not existing |

|                                                                                     | t <sub>DC</sub> / h   | 2                                               |              |

|                                                                                     | Û <sub>LI</sub> / kV  | ±1550                                           |              |

|                                                                                     | Û <sub>SI</sub> / kV  | ±1175                                           |              |

|                                                                                     | # impulse             | 15 per quadrant                                 |              |

|                                                                                     | I <sub>n</sub> / A    | 0                                               |              |

| Insulation                                                                          | U <sub>DC</sub> / kV  | ±550                                            | Not existing |

| system test                                                                         | t <sub>DC</sub> / h   | > t <sub>90</sub> = 120                         |              |

| (Superimposed im-                                                                   | Û <sub>LI</sub> / kV  | ±1550                                           |              |

| pulse voltage test                                                                  | Û <sub>SI</sub> / kV  | ±1175                                           |              |

| with "charged" di-<br>electric interfaces)                                          | # impulse             | 3 per quadrant                                  |              |

|                                                                                     | I <sub>n</sub> /A     | 5000                                            |              |

## **Design and performance verification**

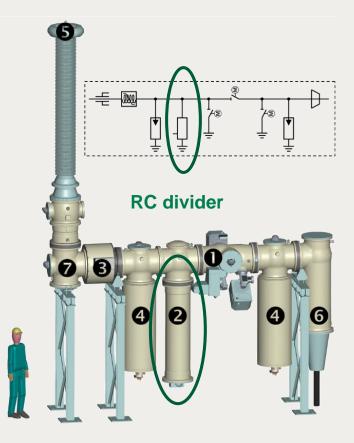

Linear voltage distribution over complete length

Distribution of (a) Voltage potential (b) Electric field

- Identical transformation ratios of the resistance part and the capacitance part to reach a flat frequency response curve

- Low-inductance capacitor design to prevent any transient overvoltage phenomena

- Divider internal insulation material must prevent charge accumulation, otherwise surface discharge can occur during impulse superposition

## **Required frequency ranges**

following the new upcoming standard CDV IEC 61869-1, Edition 2.0

#### **Basic application**

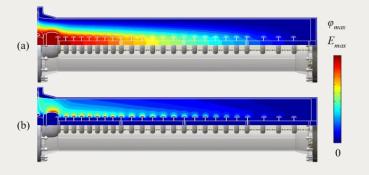

Rated DC application: requires precise measurements from DC to 3kHz – Permanent (Metering, measuring, control applications – accuracy from ±0.1% up to ±3%)

#### **Extended** application

Voltage monitoring application: up to 20kHz – Permanent (Power quality, ripple detection – accuracy from ±0,5% up to ±5%)

#### Advanced application

- Transient voltage monitoring:

- up to 500kHz for travelling wave detection application

- up to 1MHz or higher for switching impulse, lightning impulse detection

(Transient voltage detection – accuracy from  $\pm 3\%$  up to  $\pm 20\%$ )

## **Experience in Diagnostic and Monitoring application**

DC RC dividers in AIS application are in operation for more than *50 years* AC RC dividers in AIS application are in operation for at least *25 years*

#### Some examples of experience:

- Measurements of PQ parameters in many countries world-wide

- Measurements of transient voltages in DC substations

- Measurements of the ripple level in DC applications

- Measuring DC and AC voltages between power transformer and AC/DC converter (hybrid application)

- Measurements of superimposed DC voltages in AC grids f.e. in back-to-back substations

- First tests on Travelling wave detection by using voltage dividers

## Conclusion

- Dimensioning GIS RC dividers acc. to IEC 61869-15 results in an insufficient design for the expected dielectric requirements during operation

- Considering composite voltages as described by CIGRE TB 842 has a significant impact on electrical & mechanical design principles of RC dividers

- Performance of the developed RC divider design has been proven by accuracy measurements, frequency response and composite voltage testing

- Although accuracy in amplitude and waveshape is limited, the designed RC divider can be used to even measure DC+LI composite voltages