# Study Committee B4

DC Systems and Power Electronics

Paper 211 2022

# Novel HVDC MMC VSC Topology with DC Fault Current Limiting Capability

Mojtaba MOHADDES<sup>1</sup>, Shaahin FILIZADEH<sup>2</sup>, Nuwan HERATH<sup>2</sup>, Ram ADAPA<sup>3</sup>

<sup>1</sup>Transgrid Solutions. <sup>2</sup>The University of Manitoba. <sup>3</sup>FPRI

# Motivation

- Modular multilevel converters (MMCs) have become the de-facto topology for VSC-HVDC systems

- MMCs with the commonly used half-bridge submodule (SM) do not the ability to block dc faults

- Alternative converter topologies with inherent default blocking capability are desirable

# Method/Approach

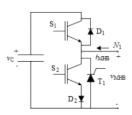

• An alternative SM topology (shown below) is proposed

The proposed SM's behavior is investigated via detailed simulations in LT-Spice, EMT simulations in PSCAD/EMTDC, and a scald-down laboratory prototype

## Notable changes with respect to the original HB SM:

Thyristor T1 replaces the anti-parallel diode of lower IGBT

Diode D2 is added in series with S2 to allow the SM to withstand negative voltage

#### **Operating States:**

ON state: S1 is triggered (current flows through either D1 or S1)

Bypass (Off) state: S2 and T1 triggered (current flow through S2 and D2 if it is positive; current flows through T1 if it is negative)

Blocked state: No trigger signal to S1, S2 and T1

## Objects of investigation

- The objective of the study is to determine, via simulations and experiments, the operating merits and limitations of the proposed MHB

- Simulation in LT-Spice consider the physics of the semiconductor devices

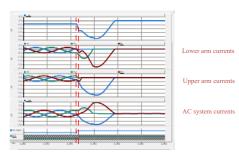

- Simulation in PSCAD/EMTDC reveal the SM-level dynamics in the context of a converter in a wider system

- Experimental results show the implementation details of the SM (at a scaled down level)

# **Experimental setup & test results**

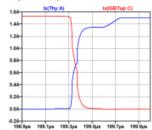

Sample of LT-Spice simulation results

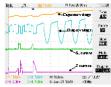

Sample of experimental results

IGBT1 and Thyristor current and voltage - Prototype

Sample of PSCAD/EMTDC results

#### Discussion

- The results obtained confirm the operation of the MHB SM

- Further validation at higher ratings is required

#### Conclusion

- The proposed MHB SM is a promising alternative to the conventional HB SM

- It offers dc-fault blocking capability and is minimally more complex than the conventional HB SM